“第010课 掌握ARM芯片时钟体系”的版本间的差异

Baiwen root(讨论 | 贡献) |

Baiwen root(讨论 | 贡献) |

||

| 第1行: | 第1行: | ||

=第001节_S3C2440时钟体系结构 = | =第001节_S3C2440时钟体系结构 = | ||

S3C2440是System On Chip(SOC),在芯片上不仅仅有CPU还有一堆外设。 | S3C2440是System On Chip(SOC),在芯片上不仅仅有CPU还有一堆外设。 | ||

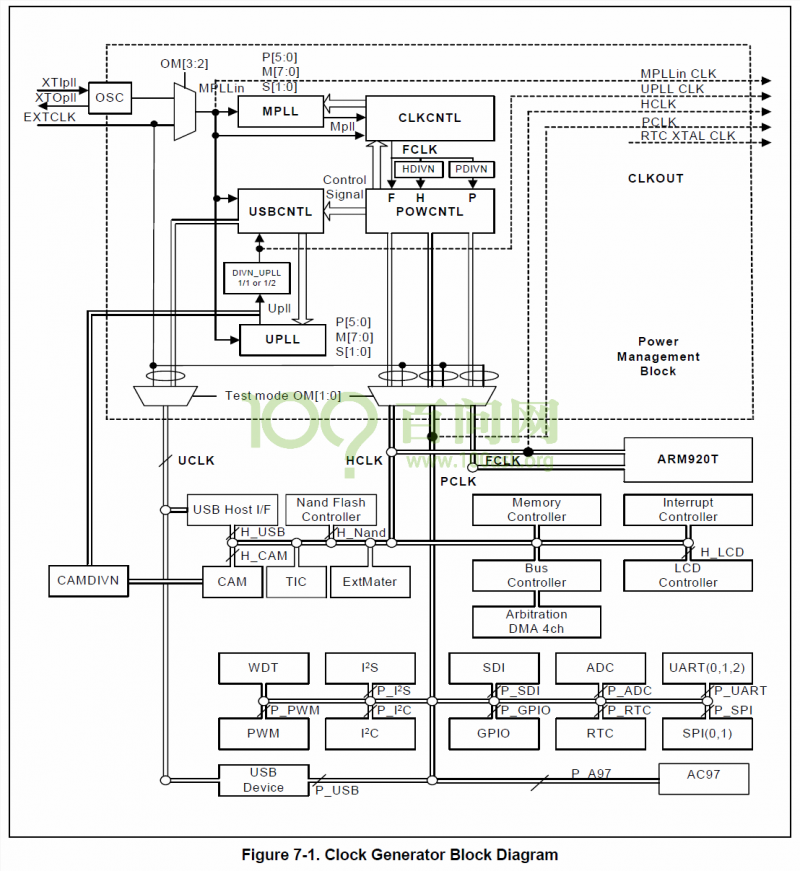

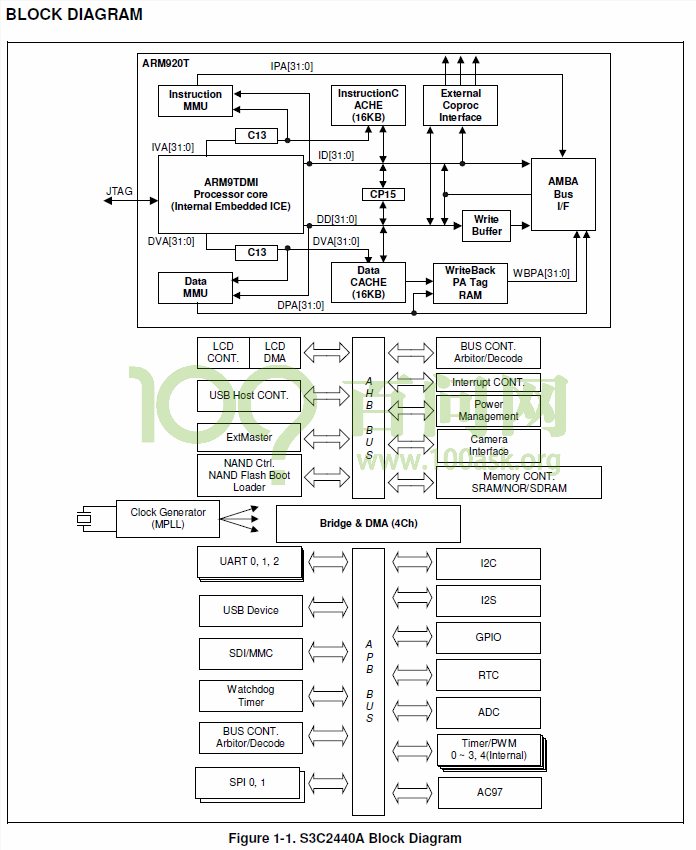

| − | + | 至于有哪些外设,可以查看参考手册。在S3C2440参考手册的第一章PRODUCT OVERVIEW里面有个BLOCK DIAGRAM图:<br> | |

[[File:chapter10_lesson1_001.png|800px]] | [[File:chapter10_lesson1_001.png|800px]] | ||

2018年1月19日 (五) 11:59的版本

第001节_S3C2440时钟体系结构

S3C2440是System On Chip(SOC),在芯片上不仅仅有CPU还有一堆外设。

至于有哪些外设,可以查看参考手册。在S3C2440参考手册的第一章PRODUCT OVERVIEW里面有个BLOCK DIAGRAM图:

可以把该图分为上中下三块,上面的是与CPU密切相关的,工作于FCLK;中间的一些对性能要求较高的设备,像LCD显示、相机等,在AHB BUS,H即为High,高速之意,工作于HCLK;下面的是一些对性能要求不那么高的低速设备,在APB BUS,P即为Peripheral之意,工作在PCLK。

在参考手册的特性里介绍了S3C2440的工作频率,Fclk最高400MHz,Hclk最高136MHz,Pclk最高68MHz。

第002节_编程提高运行时钟

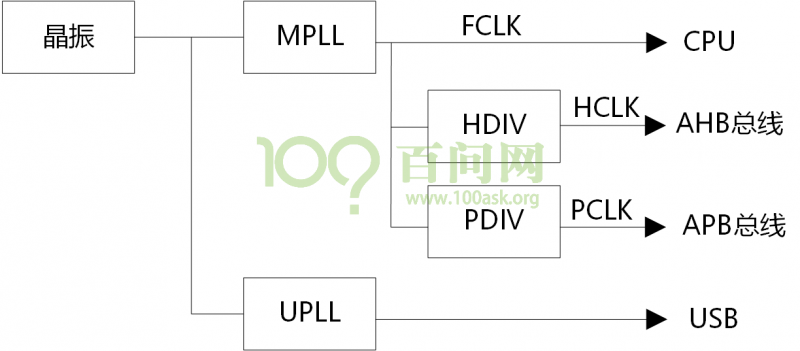

怎么编程控制MPLL、HDIV、PDIV,使FCLK=400MHz,HCLK=100MHz,PLCK=50MHz? 需要设置MPLLCON的FCLK=400MHz,设置CLKDIVN的HCLK=FCLK/4,PCLK=FCLK/8。

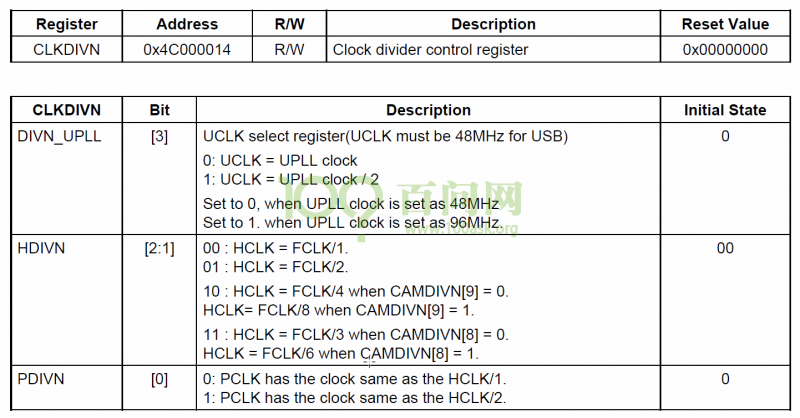

1. 首先看CLKDIVN寄存器:

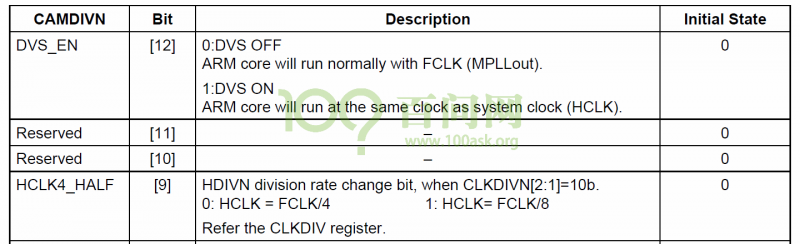

想设置HCLK=FCLK/4需要将HDIVN[2:1]设置为10,同时将CAMDIVN[9]设置为0。

查看CAMDIVN[9]的初始值默认就是0,因此只需要设置HDIVN[2:1]为10。

想设置PCLK=FCLK/8需要将PDIVN[0]设置为1,因此整个CLKDIVN寄存器设置如下:

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

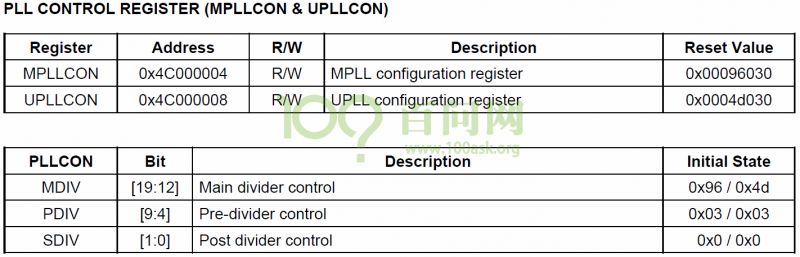

2. 现在看如何使FCLK=400MHz,在手册的PLL VALUE SELECTION TABLE里列出了常见情况PLL的设置,我们输入的是晶振的12MHz,输出需要400MHz,因此根据表格需要设置 MDIV=92(0x5C),PDIV=1,SDIV=1;

在手册介绍了MPLL的m、p、s与MDIV、PDIV、SDIV之间的关系:

Mpll = (2 * m * Fin) / (p * 2^S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

m=MDIV+8=92+8=100

p=PDIV+2=3

s=SDIV=1

MPLL=2x100x12/(3x2^1)=400MHz

因此需要配置(92<<12)|(1<<4)|(1<<0),

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

3. 此外,手册还提到,需要SetAsyncBusMode。

MMU_SetAsyncBusMode mrc p15,0,r0,c1,c0,0 orr r0,r0,#R1_nF:OR:R1_iA mcr p15,0,r0,c1,c0,0

完整的start.S:

.text

.global _start

_start:

/* 关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 设置内存: sp 栈 */

/* 分辨是nor/nand启动

* 写0到0地址, 再读出来

* 如果得到0, 表示0地址上的内容被修改了, 它对应ram, 这就是nand启动

* 否则就是nor启动

*/

mov r1, #0

ldr r0, [r1] /* 读出原来的值备份 */

str r1, [r1] /* 0->[0] */

ldr r2, [r1] /* r2=[0] */

cmp r1, r2 /* r1==r2? 如果相等表示是NAND启动 */

ldr sp, =0x40000000+4096 /* 先假设是nor启动 */

moveq sp, #4096 /* nand启动 */

streq r0, [r1] /* 恢复原来的值 */

bl main

halt:

b halt