Ethernet overview

This article gives information about the Linux® Ethernet framework, provides its composition and explains how to configure and use it.

目录

Framework purpose

以太网是将局域网或局域网中的设备连接在一起的一种方式。 以太网协议用于传输包含任何信息的数据包。

连接到网络的任何两个设备都可以通过以太网连接交换信息。 以太网提供了到路由器的快速,有效和直接的连接。

以太网可以用于许多不同的用例中,如 How to use Ethernet 部分所述:

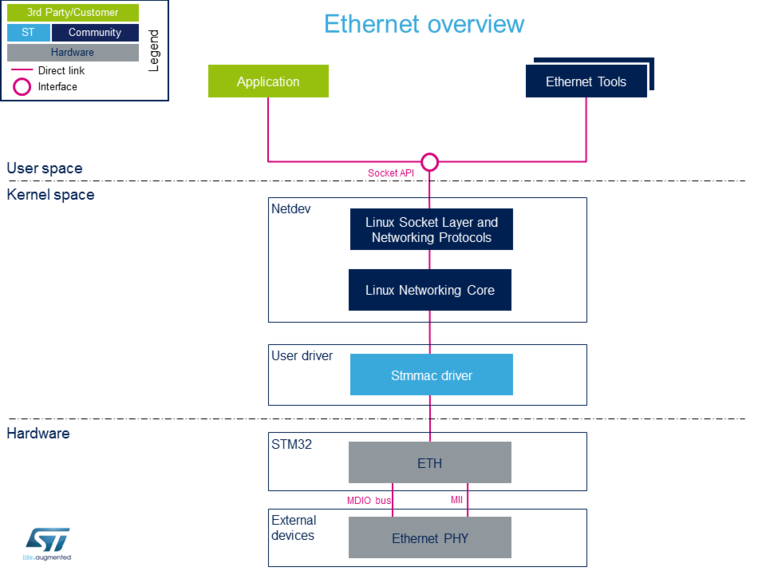

System overview

Component description

从用户空间到硬件

- 应用 (用户空间)

有很多使用以太网的应用程序: Internet浏览器,流应用程序,FTP应用程序等。

在应用程序和网络协议之间使用的主要接口是套接字

[1]

- Ethernet工具 (用户空间)

一组实用程序可用于管理和维护网络:ethtool,ping,路由,ifconfig等。

- Linux套接字层和网络协议 (内核空间)

套接字层是 [2] 一个统一的接口。 在用户进程和网络协议 [3]堆栈在内核中

- Linux网络核心 (内核空间)

内核网络层使用正在使用的传输协议来调整消息。 Linux内核的网络子系统设计为完全独立于协议。

- Stmmac驱动程序 (内核空间)

这是MAC 10/100/1000片上以太网控制器的驱动程序

(Synopsys IP块).

Documentation/networking/stmmac.txt[4]

- ETH (硬件)

这是 Ethernet IP: GMAC [5]

- Ethernet phy(以太网物理层) (硬件)

以太网PHY连接到媒体访问控制器(MAC)。 MAC控制OSI模型的数据链路层部分。

媒体无关接口(MII)定义了MAC与PHY之间的接口。

提供MII的变体(RGMII,GMII,RMII,MII),根据系统要求,它们提供的针脚数量最少且数据速率不同

MDIO总线包含两个信号:

- MDC clock: 由MAC设备驱动到PHY。

- MDIO data: 双向,它由PHY驱动,以在读取操作结束时提供寄存器数据。

以太网phy使用的连接器是RJ45。

API description

以太网API记录在Linux内核中 https://www.kernel.org/doc/html/v4.14/networking/kapi.html

Configuration

Kernel configuration

默认情况下,以太网API在ST交付中被激活。 不过,如果需要特定的配置,则可以使用Linux Menuconfig工具: Menuconfig or how to configure kernel 然后选择:

对于网络功能:

[*] Networking support --->

[*] Networking options --->

[*] Packet socket

[*] TCP/IP networking

[*] IP: kernel level autoconfiguration

[*] IP: DHCP support

[*] IP: BOOTP support

[*] IP: RARP support

[*] INET: socket monitoring interface

[*] The IPv6 protocol

[*] DNS Resolver support

对于Phy(通用PHY支持):

[*] Device Drivers --->

[*] PHY Subsystem --->

[*] PHY Core

对于STM32 DWMAC:

[*] Device Drivers --->

[*] Network device support --->

[*] Ethernet driver support --->

[*] STMicroelectronics devices

[*] STMicroelectronics 10/100/1000/EQOS Ethernet driver

[*] STMMAC Platform bus support

[*] Generic driver for DWMAC

[*] STM32 DWMAC support

Device tree configuration

DT绑定文档处理所有必需的或可选的device tree属性。

STM32内部外设的详细DT配置: Ethernet device tree configuration.

How to use Ethernet

How to use the Ethernet user space interface

请根据以下用例查看示例:

- 如何配置以太网接口: 如何配置以太网接口

- 如何执行ssh连接: How to perform ssh connection

- 如何执行ping测试: How to perform ping test

How to trace and debug the framework

How to monitor

How to monitor with sysfs

sysfs entry can be used to browse for available descriptors and hardware capabilies.

Board $> /sys/kernel/debug/stmmaceth/eth0# ls

descriptors_status dma_cap

root@stm32mp1://sys/kernel/debug/stmmaceth/eth0# cat descriptors_status

RX Queue 0:

Descriptor ring:

0 [0xf4e8d000]: 0xecb01842 0x0 0x0 0x81000000

1 [0xf4e8d010]: 0xecb02042 0x0 0x0 0x81000000

....

root@stm32mp1://sys/kernel/debug/stmmaceth/eth0# cat dma_cap

==============================

DMA HW features

==============================

10/100 Mbps: Y

1000 Mbps: Y

Half duplex: Y

Hash Filter: Y

Multiple MAC address registers: Y

PCS (TBI/SGMII/RTBI PHY interfaces): N

SMA (MDIO) Interface: Y

PMT Remote wake up: Y

PMT Magic Frame: Y

RMON module: Y

IEEE 1588-2002 Time Stamp: N

IEEE 1588-2008 Advanced Time Stamp: Y

802.3az - Energy-Efficient Ethernet (EEE): Y

AV features: Y

Checksum Offload in TX: Y

IP Checksum Offload in RX: Y

RXFIFO > 2048bytes: N

Number of Additional RX channel: 1

Number of Additional TX channel: 2

Enhanced descriptors: N

Other ways of monitoring

Ethtool is a Linux-based utility for displaying and modifying some parameters of the network interface controllers (NICs) and their device drivers.

Board $> ethtool eth0

Settings for eth0:

Supported ports: [ TP AUI BNC MII FIBRE ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Half 1000baseT/Full

Supported pause frame use: Symmetric Receive-only

Supports auto-negotiation: Yes

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Half 1000baseT/Full

Advertised pause frame use: No

Advertised auto-negotiation: Yes

Link partner advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Full

Link partner advertised pause frame use: Symmetric

Link partner advertised auto-negotiation: Yes

Speed: 1000Mb/s

Duplex: Full

Port: MII

PHYAD: 0

Transceiver: internal

Auto-negotiation: on

Supports Wake-on: ug

Wake-on: d

Current message level: 0x0000003f (63)

drv probe link timer ifdown ifup

Link detected: yes

How to trace

The Ethernet Framework (and specifically the stmmac driver) prints out information and error messages in the kernel console. They are available via dmesg command:

Board $> dmesg | grep ethernet [ 1.454632] stm32-dwmac 5800a000.ethernet: PTP uses main clock [ 1.459010] stm32-dwmac 5800a000.ethernet: no reset control found [ 1.465199] stm32-dwmac 5800a000.ethernet: No phy clock provided... [ 1.472347] stm32-dwmac 5800a000.ethernet: User ID: 0x40, Synopsys ID: 0x42 [ 1.478319] stm32-dwmac 5800a000.ethernet: DWMAC4/5 [ 1.483310] stm32-dwmac 5800a000.ethernet: DMA HW capability register supported [ 1.490564] stm32-dwmac 5800a000.ethernet: RX Checksum Offload Engine supported [ 1.497888] stm32-dwmac 5800a000.ethernet: TX Checksum insertion supported [ 1.504753] stm32-dwmac 5800a000.ethernet: Wake-Up On Lan supported [ 1.510994] stm32-dwmac 5800a000.ethernet: TSO supported [ 1.516329] stm32-dwmac 5800a000.ethernet: TSO feature enabled [ 1.522143] stm32-dwmac 5800a000.ethernet: Enable RX Mitigation via HW Watchdog Timer [ 12.356485] stm32-dwmac 5800a000.ethernet eth0: No Safety Features support found [ 12.426208] stm32-dwmac 5800a000.ethernet eth0: IEEE 1588-2008 Advanced Timestamp supported [ 12.481051] stm32-dwmac 5800a000.ethernet eth0: registered PTP clock [ 14.951370] stm32-dwmac 5800a000.ethernet eth0: Link is Up - 1Gbps/Full - flow control rx/tx

It is possible to modify the amount of 'debugging messages/data' returned by the Ethernet driver with ethtool. More documentation is available in Documentation/networking/netif-msg.txt[6] in kernel source folder.

Ethtool to set the message level:

Board $> ethtool -s eth1 msglvl [level]

How to debug

During Ethernet bring up, there are 2 frequent errors:

- DMA reset error:

[ 15.650981] dwmac4_dma_reset err [ 15.652849] stm32-dwmac 5800a000.ethernet: Failed to reset the dma [ 15.659006] stm32-dwmac 5800a000.ethernet eth0: stmmac_hw_setup: DMA engine initialization failed [ 15.668518] stm32-dwmac 5800a000.ethernet eth0: stmmac_open: Hw setup failed

When this error occurs, it is linked to the DMA Software Reset (not linked to memory transfert)

Definition of the Software Reset in GMAC specification:

When this bit is set, the MAC and the DMA controller reset the logic and all internal registers of the DMA, MTL, and MAC. This bit is automatically cleared after the reset operation is complete in all DWC_ether_qos clock domains. Before reprogramming any DWC_ether_qos register, a value of zero should be read in this bit. *Note*: The reset operation is complete only when all resets in all active clock domains are de-asserted. Therefore, it is essential that all PHY inputs clocks (applicable for the selected PHY interface) are present for software reset completion. The time to complete the software reset operation depends on the frequency of the slowest active clock. Access restriction applies. Setting 1 sets. Self-cleared. Setting 0 has no effect.

- Ethernet clock tree error:

The GMAC IP verifies that the Ethernet clock tree is well configured. When this error occurs, it is due to the Ethernet PHY that do not detect all needed clocks (tx, rx, aclk or hclk).

To solve this issue:

- check that the pinctrl of each clock is well configured - check if syscfg register is well configured (in Ethernet clock tree there are some gating/mux configured with syscfg)

Source code location

The source files are located inside the Linux kernel.

- Ethernet driver: dwmac-stm32.c[7]